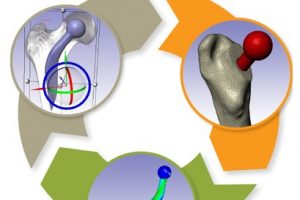

概述 植入物定位是全髋关节置换术的一个重大挑战。植入物必须要很好的适合并放置在髓管内,尽量使股骨—植入物的接触面积最大化。然而植入物位置的实验测试会超出成本的限制。另一种选择是使用计算模型在产品研发初期就综合分析植入物的位置。尽管这种方法并不是为了取代实验,但它可以帮助外科医生更好地理解植入位置对原发或继发稳定性的影响。结合 Simpleware 软件与 ANSYS 创建自动化的工作流程,整合 CAD 设计的植入物和股骨 CT 扫描,生成用于微动分析的有限元模型。模拟结果生成的响应面证实了位置变化对微动的影响。 亮点 在Simpleware软件中整合CAD植入物和股骨CT扫描在Simpleware软件中生成FE网格通过脚本自动生成多组植入物位置/方向在ANSYS Workbench中进行植入物微动的模拟对结果进行后处理并生成响应面预测植入物位置的最佳和最差情况 图像处理和CAD整合 使用Simpleware ScanIP和Simpleware CAD将由CT扫描进一步处理获得的分割后的股骨模型与CAD设计的植入物结合。然后利用Simpleware FE生成有限元网格,导出至ANSYS Workbench中进行微动模拟。通过Simpleware API运用Python脚本自动生成多个植入位置,而无需耗费大量时间手动调整。 图:使用Simpleware CAD将分割后的股骨与CAD设计的植入物结合 FE网格生成 在本例中,为每个植入位置生成有的限元网格包含股骨的约10000个节点和38000个单元,钛金属植入物模型约2000个节点和6000个单元。采用Simpleware软件的自动转换算法基于原始扫描的CT值(Hounsfield单位,HU)为股骨分配标准材料属性。为模拟约束和加载条件给植入物和股骨添加节点集,在植入物—骨界面处的网格细化也增加了模拟的真实性。 图:使用Simpleware FE对股骨和植入物进行网格划分 应力分析&响应面模型 将初始的有限元模型导出至ANSYS Workbench,在上千个可能的候选的基础上产生成功的微动模拟。利用Kriging回归法对425个成功模拟点进行插值,生成响应面模型(RSM)。 ANSYS Workbench模拟可以利用RSM确定导致微动最高和最低可能值对应的植入位置。外科医生可以根据这些结果解释和预测植入物的最佳和最差位置。 图:在ANSYS Workbench中获得的最佳位置(左)和最差位置(右) 结果:最佳/最差的植入位置 利用Simpleware软件和ANSYS结合图像数据与有限元分析,成功地开发了一种用于分析植入物与股骨间相互作用的自动化工具。采用的响应面方法使人们深入了解微动对定位的敏感性。 随着该工具可行性的建立,进一步的工作可以集中在研究多个植入物设计在患者群体的分析。因此除了植入物研发之外,该工具在手术规划方面也有非常重要的应用。 参考 致谢和更多信息请参考英文原文:https://www.synopsys.com/simpleware/resources/case-studies/total-hip-replacement.html。

超薄砷化镓晶体管的性能极限【QuantumATK亮点文章】

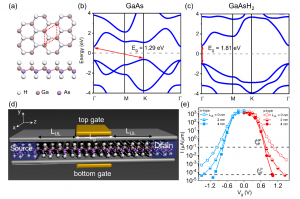

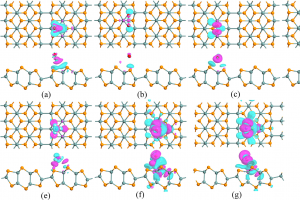

背景 晶体管的尺寸微缩是推动微电子电路发展的关键。然而,由于严重的短沟道效应,传统硅基晶体管正在接近其物理极限。当栅极长度小于 10 纳米时,实验制备的硅基晶体管的已经不能满足国际半导体技术发展路线图(ITRS)的开电流标准。为了延续摩尔定律,目前主流的一种解决方案是将沟道替换为更高迁移率的材料。其中,III-V 化合物半导体有着比硅更高的电子迁移率和电子注入速度,被认为是硅的有力继任者。而砷化镓(GaAs)因其具有良好的n型和p型器件性能,在一系列 III-V 半导体中脱颖而出。为了尽可能延长摩尔定律的寿命,探索n型和p型GaAs晶体管的性能极限十分必要。 研究内容 具有较薄沟道的晶体管可以进一步增强栅极控制力和对短沟道效应的免疫力。单层氢化 GaAs(ML GaAsH2)是超薄 GaAs 的极限形式,因此,模拟 ML GaAsH2 金属氧化物半导体场效应晶体管(MOSFET)可以给出超薄 GaAs FET 的性能上限。本文报道了作者对 n 型和 p 型双栅 ML GaAsH2 MOSFET 的第一性原理与量子输运模拟研究。作者引入 underlap 结构,得到了器件从5纳米栅长一直微缩至 1 纳米的转移特性。 图1 (a) ML GaAsH2 结构图。(b、c) ML GaAs 和 ML GaAsH2 的能带结构。(d) 双栅 ML GaAsH2 MOSFET 的示意图。(e) 5 纳米栅长的转移特性曲线 作者发现,n 和 p 型ML GaAsH2 晶体管的性能极限分别位于 3(4)和3(5)nm 栅长处。与其他模拟工作中的典型二维器件进行横向对比,只有 ML GaAsH2 器件的开电流在亚 5 纳米栅长范围内,可以同时满足NMOS、PMOS 在高性能、低功耗应用下的 ITRS […]

磁性与自旋电子学研究案例集(三)

用 Y 位原子替代 Heusler 晶格实现自旋阀的巨磁电阻 ”全Heusler”自旋阀由两个半金属 Heusler 电极和一个非磁性 Heusler 隔断构成,其中包含两个对磁电阻有重要影响的界面。为了减少界面无序度,保护电极在同一区域的半金属性,作者提出了一种方案,通过替换半金属Heusler电极中的Y位原子来构建自旋阀,以获得基于 Slater–Pauling 规则的相应非磁性隔断结构。这样,可以自然地确保两种材料的晶格和带匹配。以 Co2FeAl 为电极,Co2ScAl 为间隔材料,构建了Co2FeAl/Co2ScAl/Co2FeAl(001)自旋阀。基于第一性原理计算,从声子谱和形成能两方面确定了当间隔基 Co2ScAl 生长在电极材料 Co2FeAl 终止的(001)表面时,FeAl/CoCo 界面最稳定。通过将界面原子的投影态密度与体电极材料的相应态密度进行比较,只有Al的自旋上升态值在置换前后从 0.17 态/原子/eV变为 0.06 态/原子/eV,界面处的半金属丰度保持不变。结果表明,自旋相关的输运性质显示出显著的理论磁电阻 MRop,可以达到1010%,远大于以前报道的106%。(Zhang, Lei, Binyuan Zhang, Liwei Jiang, and Yisong Zheng. “Giant magnetoresistance in spin valves realized by substituting Y-site atoms in Heusler lattice.” Journal of Physics: Condensed Matter 34, no. 20 (2022): […]

逆向工程在汽车零部件设计中的应用【Simpleware应用】

概述 考虑到所用材料的复杂性和处理图像数据时对精度的需求,对汽车零部件进行逆向工程和分析是一个很大的挑战。 在本项目中,研究人员利用Simpleware ScanIP克服上述困难,将气缸盖的CT数据转换为适合检测缺陷和可导出为模拟准备的网格化高质量三维模型 为进行热模拟分析和考虑到铸造铝件时空洞的影响,因此将重点放在气门座的分割上。 亮点 从CT扫描获得3D图像数据在Simpleware ScanIP中进行可视化和初始分割使用形态学开滤波器和3D编辑工具改善气门座的分割在Simpleware FE中对处理后的图像数据进行网格划分将为模拟准备好的网格导出至LS-DYNA®进行热结构分析 可视化和图像分割 利用工业CT扫描设备以0.4mm×0.4mm×0.5mm的分辨率获取气缸盖的成像数据,并导入Simpleware ScanIP中。利用体积渲染、不透明度设置和颜色映射工具根据其底层灰度值进行可视化和重建数据,故此能够检测到铸件中微小缺陷/空洞。下一步的分割要将气门座与气缸分开。 气门座的3D编辑 在Simpleware ScanIP中,使用多种图像处理工具的组合将气门座从气缸盖中分割出来。初始阈值可以快速为各组件创建独立的掩模,在选中的感兴趣区域(ROI)使用形态学滤波器处理模型。利用Simpleware的3D编辑工具,在气门座周围创建一个3D ROI,用形态学开放滤波器去除小范围的噪声。这些工具使气缸盖中气门座的多部位分割更加准确和清晰。 图:使用Simpleware的3D编辑工具去除气门座周围的小范围噪声 结果 采用Simpleware FE对分割后的图像数据进行网格划分,并导入LS-DYNA®初步分析气缸盖中有无空洞对图像的影响。在考虑进气温度和排气温度的情况下, 比较有无空洞时空洞周围的主应力。该方法有助于深入了解零件在不同制造条件下的潜在性能,为缺陷分析奠定了未来研究的基础。 图:在LS-DYNA中分析气缸盖中有无空洞所造成的影响 参考 致谢与其他信息请参考英文原文。

探究睡眠呼吸暂停【Simpleware应用】

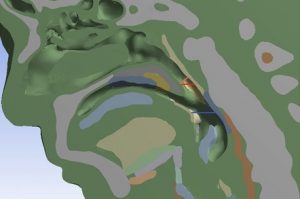

概述 理解如何维持气道通畅的基础是咽部被动机械变形对上气道塌陷的作用进行分析。本项研究首先在 Simpleware 软件中使用 CT 扫描数据创建了精细的 3D 解剖模型,然后采用有限元分析(FEA)方法研究变形情况。结果与体内试验及文献报道吻合较好,可以作为更全面地模拟人上气道塌陷和治疗阻塞性睡眠呼吸暂停的起点。 亮点 从 CT 获取人体上气道图像数据在 Simpleware ScanIP 中重建 36 个不同的解剖结构在 Simpleware FE 中生成有限元网格并施加内气道压力边界条件在 ANSYS Workbench 中进行气道变形模拟 图像处理和网格生成 采用多层螺旋 CT 扫描仪获取一例 79 岁男性的正常气道 CT 扫描数据。通过 Simpleware ScanIP 对 DICOM 文件进行三维重建和分析。对整个图像应用二值化的中值滤波以降低噪声;采用噪声曲率流滤波器促进区域内平滑、抑制区域间平滑、去除噪声,增强灰度边界。对36个单独的组织、骨骼、软骨、韧带、肌肉和膜的解剖结构进行分割。采用递归高斯平滑对分割后的结构进行平滑处理,进一步降低噪声水平,减弱锐利的边缘。将模型的下侧裁剪至声带附近,从而减少 FEA 的计算需求。 图:用于 FEA 的三维模型渲染图。每个数字和不同颜色代表特定的解剖结构。 使用 Simpleware FE 创建由正四面体单元组成的网格,进行局部网格细化和额外的网格改进措施。多部分网格在接触界面上具有共享节点,在气道壁上定义的节点集施加内气道压力边界条件,并在立方体域边界与模型的界面处定义节点集;在这里也采用了固定边界条件。 模拟结果 划分的网格和节点集以 .cdb 格式导入 ANSYS Workbench 进行模拟。在 Image J 中分析横截面积,证明网格已收敛。在小变形的限制下估算被动咽部组织的性质,以线性弹性作为合理假设。 在不同气道压力下分析口咽部和腭咽的横截面积,确定大气压(零)附近的面积随压力的变化斜率,并与已发表的放松状态下已麻醉正常人的体内实验数据进行比较。研究结果提供了新的理解,有助于进一步基于图像建模研究,也有助于针对口腔压力治疗设备进行新型医疗器械设计。 图:在基于三维 CT 的人咽部有限元模型中,整体和定向局部变形的矢状断面视图。(A)总变形;(B)横向变形;(C)前后向变形;和(D)垂直向变形 参考 致谢请参考英文原文;Carrigy, N.B. et al., 2016. Simulation of muscle and adipose tissue deformation in the passive human pharynx. Comput Methods Biomech […]

传感器材料与器件的模拟【QuantumATK亮点文章】

基于高导电碳纳米管/聚氨酯复合纤维的可穿戴式应变传感器 高导电性和可伸缩性纤维因其在柔性可穿戴电子设备中的潜在应用而受到越来越多的关注。羧基化碳纳米管(c-CNT)被涂覆在柔性纤维上,作为制造可穿戴式应变传感器的方便方法。然而,由于碳纳米管的石墨化结构在羧化过程中被破坏,碳纳米管的导电性降低。如何让 c-CNT 复合纤维具有高导电性仍然是一个重大挑战。此研究通过在聚氨酯(PU)纤维上涂覆金属离子连接的 c-CNT 来制备高导电纤维,以提高 c-CNT 之间的电子传输速率。由 Fe2+ 离子和羧基形成的金属配位结显著提高了 PU 的导电性 /CNT@Fe2+ 纤维(高达 72 S m−1). 密度泛函理论计算证明,这种高导电性是具有强电子态耦合的配位结促进电子输运的结果。由此产生的配位效应增强了碳纳米管之间的相互作用,使导电网络更加灵活。基于聚氨酯的应变传感器/CNT@Fe2+ 纤维具有高灵敏度(50% 应变下的规范系数为 36)、大应变范围、不明显的漂移和耐久性。纤维应变传感器成功地用于监测关节运动和面部表情。【Zaiyu Zhuang, et al. Nanotechnology 31 (2020) 205701】 应变和电场作用下小分子在GeP单分子膜上的可调吸附行为 作者使用第一性原理计算方法研究了 GeP 单层膜对小气体分子(CO、CO2、O2、H2O、NH3、NO 和NO2)的传感特性。根据计算的吸附距离、吸附能和电荷转移,作者发现 GeP 单层膜对 NO2 和 NO 分子最敏感,所有气体分子都作为受体从 GeP 单层膜中获得电子。NO2 分子的吸附能小于 NO 分子的吸附能,这意味着 NO2 更容易从 GeP 中解吸。不同的功函数变化也表明了在无氧环境中识别 NO2 和 NO 的可能性。此外,作者将单轴和双轴应变应用于 GeP 单层膜,发现较小的双轴压缩应变可以有效地提高基于功函数型传感器的 GeP 对 […]

增材制造个性化骨增量钛网的工程实现【Simpleware应用】

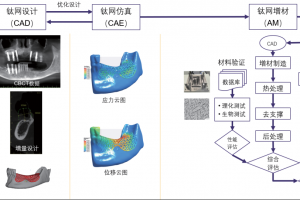

简介 引导骨组织再生(guided bone regeneration,GBR)是一种口腔种植骨增量技术,在骨缺损区利用屏障膜维持空间并阻挡增殖较快的上皮细胞和成纤维细胞长入,保证增殖速度较慢的成骨细胞优势增长而形成骨。随着增材制造(常被称为“3D打印”)技术的发展,可利用计算机辅助设计(computer aided design,CAD)设计出与患者颌骨形态贴合并且具有预期骨增量水平的个性化钛网模型,在激光的作用下通过材料逐层累积将其“打印”出来,最终将这种个性化骨增量钛网用于引导骨组织再生手术。与传统钛网相比,增材制造的个性化骨增量钛网更加贴合骨缺损部位,极大缩短手术时长并降低钛网暴露率,尤其适用于大面积、解剖形态复杂的骨缺损病例。 个性化骨增量钛网工艺研发 对于增材制造个性化骨增量钛网产品,研发工程师与口腔种植科的临床医生和影像科医生组建钛网项目团队,经由主治医生获得患者的影像数据(CBCT产生的“.DICOM”数据)及其对患者预期骨增量的要求,同时主治医生还会提供患者的口内扫描数据、修复体和种植体规划数据等作为钛网设计的参考模型。研发工程师将“.DICOM”数据导入到Simpleware Scan IP软件中进行解剖结构的三维模型重建,包括患者骨缺损处的颌骨、邻牙及牙根、神经管(下颌病例)并将其导出为“.STL”格式的三维模型。使用光敏树脂材料将带邻牙的颌骨模型增材制造出来,用于个性化骨增量钛网的试配。以口腔修复为导向,根据主治医生预期骨增量要求,以及钛网与邻牙、神经等解剖结构的位置关系,同时考虑固定钛网用的钛钉尺寸和位置,设计出钛网的轮廓面。在Solidworks 软件中将钛网网孔的单胞结构填充于钛网轮廓面上并增加钛网的厚度为0.3~0.4 mm,导出“.STL”格式的钛网模型。下图显示了个性化骨增量钛网的设计模型及其与颌骨、钛钉和骨粉配合在一起的示意图。个性化设计出来的钛网模型可以进行有限元分析和静力学计算,以评估钛网植入后的生物力学性能。 图:个性化骨增量钛网的增材制造 图:个性化骨增量钛网设计模型,包括有严重骨缺损的下颌骨、个性化骨增量钛网、钛网固定钛钉和人工骨粉 在完成钛网的CAD设计和CAE仿真后,将钛网模型(“.STL”格式)进行增材制造工艺支撑和打印布局的设计,钛网及其工艺支撑按照25μm厚度进行切片,切片后的数据导入至增材制造设备MLab中,使用医用纯钛材料进行增材制造,所得产品在热处理后进行线切割和去支撑,经过打磨后进行喷砂处理,最后进行超声清洗以及灭菌杀毒,使用无菌包装将其封闭。主治医生在种植手术时将个性化骨增量钛网拆除包装直接植入患者口腔,在手术完成后拍摄即刻CBCT。 骨缺损颌骨三维重建和个性化骨增量钛网设计 根据每位患者的CBCT数据三维重建生成骨缺损颌骨模型,使用光敏树脂材料增材制造出用于个性化骨增量钛网试配和术前评估;依据临床要求对骨缺损颌骨进行“数字雕刻”,即通过模拟现实中蜡型雕刻方式制作数字化的模型,设计出满足预期骨增量要求的“完美”颌骨,在此基础上完成个性化骨增量钛网的模型设计。相较于传统钛网,采用“全程数字化”技术设计和制造的个性化骨增量钛网更贴合患者牙槽骨形态,避免了术中需要折弯剪裁的复杂步骤,节省大量手术时间;个性化骨增量钛网适合多种复杂骨缺损病症,为引导骨再生手术提供稳定的成骨空间,实现了种植术后功能重建和美学的可预期性。 图:由患者CBCT数据重建而成的骨缺损颌骨和个性化骨增量钛网模型 为了提高设计效率同时有效减小“金属伪影”对模型尺寸精度的影响,工程师开发出基于神经网络的深度学习算法,对目前已处理的200多例患者CBCT数据进行精准标注和训练,产生预训练模型用于解剖结构的分割、检测和分类任务,最终实现自动生成骨缺损颌骨和邻牙的精准三维模型。 结论 根据患者的解剖结构和预期的骨增量水平定制式设计出个性化骨增量钛网,通过有限元分析对钛网的设计模型进行验证,通过增材制造的工艺将其生产出来,同时在生产过程中增加“随炉试样”用以验证钛网成品的理化性能。增材制造的个性化骨增量钛网可以获得满足临床应用要求的性能,其临床上的长期有效性有待钛网植入后进一步的随访观察。 参考 张立强:增材制造个性化骨增量钛网的工程实现。中国口腔种植学杂志 2021 年 12 月第 26 卷第 6 期,第354~361页。

基于CrI3的磁隧穿结中磁阻的层数依赖行为【QuantumATK亮点文章】

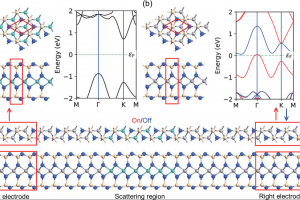

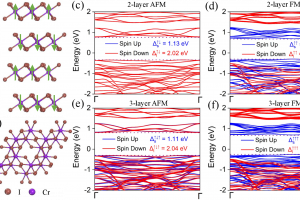

简介 磁隧穿结广泛应用于磁头、磁随机存储器等自旋电子学器件中,其磁电阻大小直接决定了器件的存储密度大小。基于二维磁性材料的磁隧穿结相比于传统的基于块体的磁隧穿结,由于具有表面平整无悬挂键等优点,在磁电阻上表现出明显的优势。目前实验上已经在以 2 层、3 层,4 层和 10 层 CrI3 为隧穿层的磁隧穿结中观测到了 310%、2000%、8600% 和 106 %的磁电阻,其中的最大值远远高于传统的基于 MgO 隧穿层的磁隧穿结(1000%)。因此,系统地研究基于二维磁性材料的磁隧穿结中磁电阻随层数的变化关系,将有助于突破目前磁隧穿密度的极限。基于此,北京大学吕劲研究员和杨金波教授课题组合作,采用第一性原理结合非平衡格林函数的方法,系统计算了以 2~12 层 CrI3 为隧穿层,以 Ag 为电极的磁隧穿结中的磁电阻变化,同时也探究了偏压、磁化方向等因素对磁电阻的影响。该研究结果为发展具有更高磁存储密度的低维自旋电子学器件提供了新的思路。 图1. CrI3晶格结构与不同层数和磁序下的能带结构 CrI3是一种层内铁磁耦合,层间反铁磁耦合的二维范德华磁性半导体。由于层间耦合较弱,其自旋分辨的能隙随层数变化较小。在以Ag为电极,以CrI3为隧穿层的磁隧穿结中,铁磁态的电导远远高于反铁磁的电导,且铁磁态情形下能够获得接近100%的自旋极化率。铁磁态电导随层数呈现奇偶振荡的变化趋势,而反铁磁态的自旋极化率则随层数呈现奇偶振荡的趋势。 图2. Ag/2~12层CrI3/Ag磁隧穿结结构示意图;电导、自旋极化率随层数变化情况 作者发现,以Ag的电极的磁隧穿结的磁电阻在7层以下呈奇偶振荡的变化的趋势,在7层以上则是呈单调递增的趋势,在12层CrI3的器件中获得了高达109%的磁电阻。通过与以石墨为电极的磁隧穿结计算结果的对比,以及对投影局域态密度的分析,作者图1. CrI3晶格结构与不同层数和磁序下的能带结构发现由金属电极引起的邻近CrI3层的金属化是引起磁电阻奇偶振荡的原因。 图3. 不同磁隧穿结中磁电阻随层数变化情况 图4. 不同电极情况下自旋分辨的投影局域态密度(以4层CrI3为例) 总结 本文利用QuantumATK软件,研究了基于二维CrI3的磁隧穿结的量子输运。研究发现,隧穿磁电阻与隧穿层层数大致呈正相关关系,计算获得了最高达到109%的磁电阻。另外,磁隧穿结中的金属电极是造成隧穿磁电阻振荡的关键。该工作证明了二维磁性材料在自旋电子学研究中的潜力,明确了层数对磁电阻的影响,对器件的实验实现具有指导意义。 参考文献 B. Wu, J. Yang, R. Quhe, S. Liu, C. Yang, Q. Li, J. Ma, Y. Peng, S. Fang, J. Shi, J. Yang, J. Lu […]

孔径对颗粒基催化剂流动的影响

概述 硅铝颗粒基催化剂中孔隙结构对大尺度(约104 m)流体流动的影响对于了解其性能具有非常重要的意义。本项目采用多尺度层析成像(MT)方法获取催化剂颗粒从纳米到毫米尺度的图像。所用试样均在不同温度下烧结/煅烧。 将图像导入 Simpleware 软件中进行分析和分割,对纳米/微米结构中每种长度尺度划分网格。为研究不同孔径对流动的影响,在 ANSYS Fluent 中进行渗透率计算,使人们对催化剂的输运性质有新的认知。 亮点 由 XMT、DBFIB / FIBSEM 和 ET 获得不同长度尺度的三维数据将数据分割成二值化数据集使用 Simpleware FE 为每种长度尺度的复杂纳米/微米结构生成 CFD 网格在 ANSYS Fluent 中计算渗透率模拟与实验测试相结合,确定孔隙率对流动的影响 图像采集 将两种颗粒基催化剂挤压成三叶状颗粒,在不同温度下煅烧生成2个样品并扫描。采用同步辐射X射线三维成像(XMT)、双束聚焦离子层析成像术(DBFIB)和电子断层三维重构(ET)获得不同长度尺度的三维图像。 在3D层析成像重建后对数据进行处理,减少噪音和分割块体材料与空洞,从而得到一个二值化的数据集。对颗粒样品也进行了实验测量以确定渗透率。 图:不同层析技术下其典型体素长度尺度的表征 图像处理&网格化 为模拟流经催化剂颗粒的渗透率,使用 MATLAB® 镜像层析体积,结合 Simpleware ScanIP 和 Simpleware FE 将每种长度尺度的纳米/微米结构转换为体积网格。利用填充工具选择感兴趣区域,流体边界界面处的网格划分要比块体精细,并在网格的上下游方向添加缓冲区以便导出至 ANSYS Fluent 为渗透率的 CFD 分析做好准备。将较精细长度尺度的模拟结果输入到下一个长度尺度的结构中,直至模拟考虑了催化剂中的所有相关尺度。 图:Simpleware FE中S2催化剂颗粒(红色孔隙)微观结构的多部分网格划分 模拟&结果 分析证实:与在较高温度下烧结的催化剂相比,经过较低温度烧结的催化剂颗粒是如何产生更大、更开放且具有更好连通性的孔隙结构。 存在更开放的孔隙结构使得活性位点间的渗透性和流动性更好,从而增强催化剂性能。因此,通过 MT 获得不同长度尺度孔隙结构的流体流动研究为未来催化剂性能的定制化和改进其他能源材料的广泛应用提供了基础。 图:跨长度尺度的孔隙率示例:将体积A的渗透率(K)融入体积B的主体

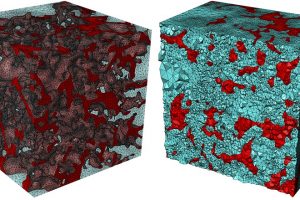

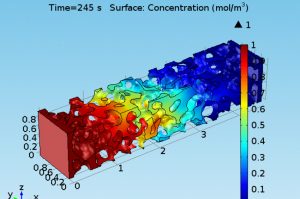

模拟孔隙尺度的化学输运

概述 基于图像的建模可用于分析通过多孔介质的传质现象,特别适用于储层岩石孔隙-喉道网络。这些分析的目的是为提高我们对流体通过可变孔隙尺度运动方式的理解和表征。 本项目使用真实结构的 micro-CT 图像数据,在 Simpleware 软件中进行可视化和处理,生成网格化的3D模型,然后将其导出至 COMSOL Multiphysics®中研究化学输运机制。 亮点 从开源库中获取真实岩石结构的 micro-CT 数据在 Simpleware ScanIP 中进行图像处理和分割在 Simpleware FE 中为孔隙结构生成高质量的多相网格在 COMSOL Multiphysics 中进行孔隙尺度化学输运模拟 图像处理 使用帝国理工学院孔隙尺度模型(PERM)联盟提供的开源岩石 CT 图像库中的 micro-CT 数据,获得孔隙空间和微观结构的 RAW 图像文件。在 Simpleware ScanIP 中将图像数据转换为基于 3D 体素的几何结构,为网格划分做准备。由于 CT 扫描通常会产生噪音,此步骤的处理极其复杂。为了渲染构造良好的岩石和孔隙相,在 ScanIP 软件中使用了一系列的视觉滤波器和图像处理技术。 图:Simpleware ScanIP中micro-CT数据的可视化和分割 利用 Simpleware FE 模块为多相流模型生成非常稳健的 CFD 网格,并直接导出至 COMSOL Multiphysics。 图:使用Simpleware FE模块生成网格化的多孔结构模型 然后将网格化的多孔介质模型导入商用偏微分方程(PDE)求解器 COMSOL Multiphysics® 中求解 […]