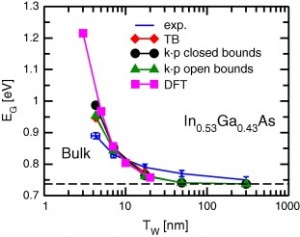

由 Synopsys QuantumWise, ETH Zürich, Università degli studi di Udine, Università degli studi di Bologna 以及IBM Zürich Research Laboratory 共同发表在 Solid-State Electronics 杂志上的文章(http://dx.doi.org/10.1016/j.sse.2015.09.005)报道了最新的关于III-V族半导体量子井的研究,评估了III-V族半导体的能带计算方法以及用于器件模拟的能带校正参数。 文章摘要 我们详细的比较了用非抛物线有效质量模型结合密度泛函理论、紧束缚方法、k·p 方法等进行能带结构计算的结果。在提取了InAs、GaAs、InGaAs等体系的用于非抛物线型Γ、L、X谷和谷间带隙参数组合之后,考察了厚度从 3 nm 到 10 nm 的量子阱以及带隙对薄膜厚度的依赖性,并与实验中In_{0.53}Ga_{0.47}As 的量子阱进行了比较。能带结构对MOSFET的源漏电流的影响则由弹道输运模型模拟。得到的结果为评估III-V族半导体能带结构计算方法和为器件计算进行能带校正参数提供了严格的依据。 Simulated and experimental energy gap for unstrained In_{0.53}Ga_{0.47}As quantum well on Al2O3. 更多关于 III-V-MOS 计划的信息: http://quantumwise.com/about-us/projects

近期活动日历

周日周一周二周三周四周五周六日一二三四五六3031123456789101112131415161718192021222324252627282930123近期活动列表

- 没有活动

- 所有活动

标签

关于费米科技

费米科技以促进工业级模拟与仿真的应用为宗旨,致力于推广基于原子级别模拟技术和基于图像模型的仿真技术,为学术和工业研究机构提供研发咨询、软件部署、技术攻关等全方位的服务。费米科技提供的模拟方案具有面向应用、模型新颖、功能丰富、计算高效、简单易用的特点,已经服务于众多的学术和工业用户。

-

最近更新

- 水滑石/硼酸锌/改性环氧树脂复合阻燃涂层的制备及其阻燃性能 2025年4月25日

- Co-TMDC 磁性隧道结:自旋电子学的新前沿 2025年4月18日

- 锂电池电极建模:基于 CT vs DFN 模型 2025年4月14日

- 【辽宁工程技术大学】褐煤在ReaxFF MD高温条件下的燃烧机理分析(Fuel 2025) 2025年4月12日

联系方式

- 留言板:点击留言

- 邮箱:sales_at_fermitech.com.cn

- 电话:010-80393990

- QQ: 1732167264

订阅费米科技新闻

- 邮件订阅:

您可以使用常用的邮件地址接收费米科技定期发送的产品更新和新闻。

点击这里马上订阅! - 微信订阅:

微信扫描右侧二维码。

- 邮件订阅: