简介

构建互补金属氧化物半导体(CMOS)器件需要 n 型和 p 型金属氧化物半导体场效应晶体管(MOSFETs)。但在超短栅长情况下寻找一种 n 型掺杂和 p 型掺杂同时满足国际半导体技术路线图(ITRS)标准的沟道材料仍然是一个挑战。最近合成的二维晶体 $\mathrm{WSi}_2\mathrm{N}_4$ 具有较高的空穴和电子载流子迁移率,为这一问题提供了可能的解决方案 [Science, 2020, 369 (6504), 670-674]。北京大学物理学院吕劲课题组使用第一性原理密度泛函理论(DFT)和非平衡格林函数(NEGF)方法,探讨了双栅单层 $\mathrm{WSi}_2\mathrm{N}_4$ MOSFETs 在亚 5 nm 栅长下的性能极限 [Phys. Rev. Appl., 2023, 20 (6), 064044]。这项研究显示,n型和p型双栅单层 $\mathrm{WSi}_2\mathrm{N}_4$ MOSFETs 可将满足ITRS高性能(HP)标准的门长尺寸缩短为 3 nm,开态电流高度对称。在功耗延迟积(PDP)与延迟时间($\tau$)的多目标优化 Pareto 边界分析中,n 型单层 $\mathrm{WSi}_2\mathrm{N}_4$ 晶体管处于典型二维材料中最优平衡的 Pareto 边界上。显示了单层 $\mathrm{WSi}_2\mathrm{N}_4$ 作为下一代 CMOS 器件沟道材料的潜力。考虑温度和无序的影响,模拟结果仍然适用。该项工作于今年12月发表在 Physical Review Applied 上,北京大学物理学院博士生黎颖为第一作者,北京大学物理学院吕劲研究员和洛阳师范学院化学化工学院副教授、哈佛大学 John A. Paulson 工程与应用科学学院访问学者孙晓甜为共同通讯作者。

研究内容

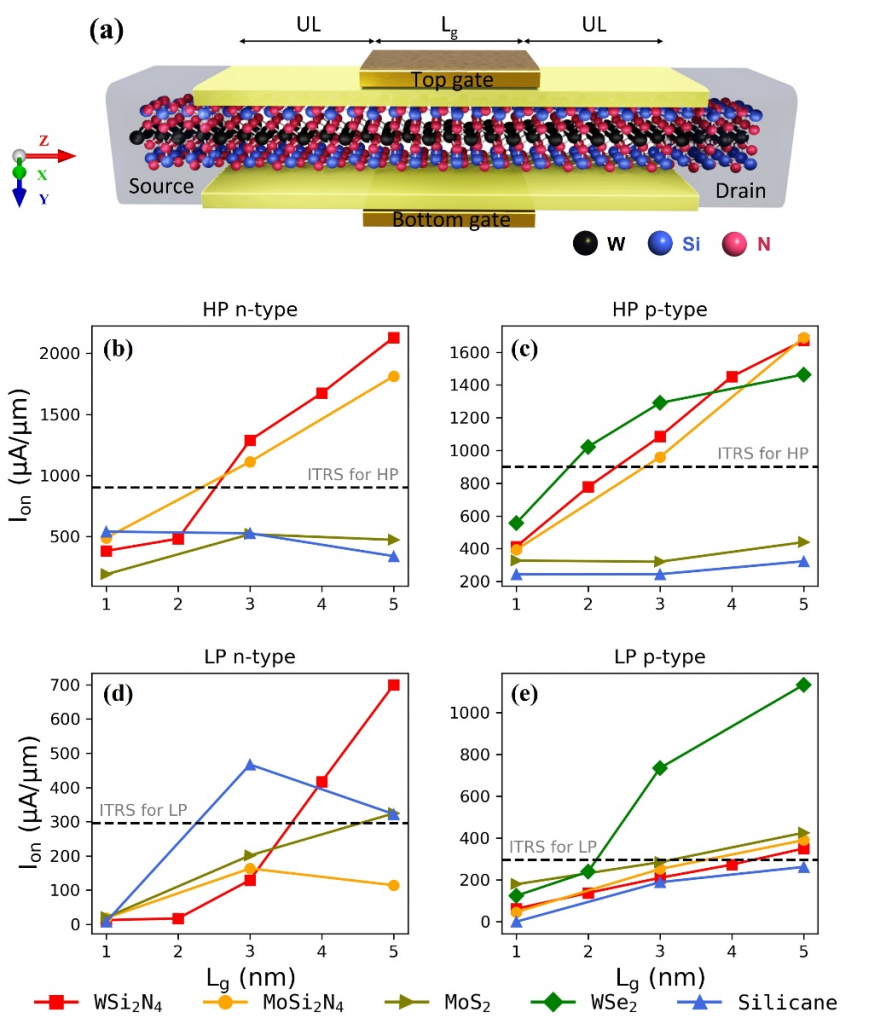

本研究通过掺杂浓度和欠叠层结构对亚 5 nm 栅长双栅单层 $\mathrm{WSi}_2\mathrm{N}_4$ MOSFETs 的输运性能进行优化。高性能单层 $\mathrm{WSi}_2\mathrm{N}_4$ 晶体管的开态电流显著高于相同栅极长度的单层 $\mathrm{MoS}_2$ 晶体管,整体略高于结构相似的单层 $\mathrm{MoSi}_2\mathrm{N}_4$ 晶体管,n 型和 p 型器件的最大开态电流分别达到 2130 μA/μm 和 1672 μA/μm。p 型低功耗(LP)单层 $\mathrm{WSi}_2\mathrm{N}_4$ 晶体管的最大开态电流可达 700 μA/μm,是同类单层 $\mathrm{MoSi}_2\mathrm{N}_4$ 晶体管最大开态电流的 6.1 倍。

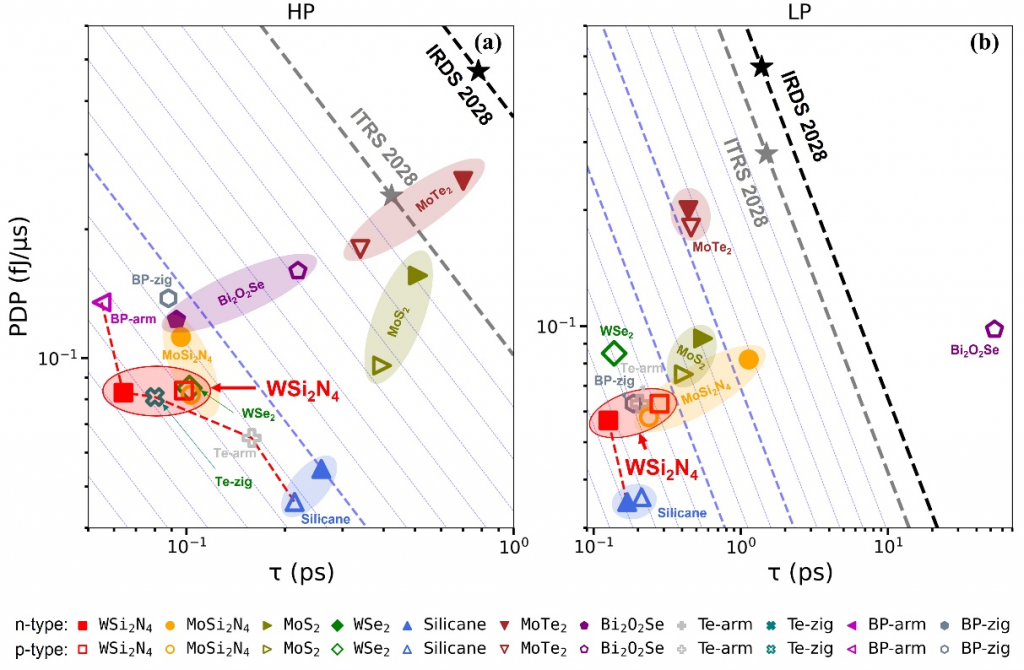

在晶体管的设计中,单次开关切换的功耗与时间是两个重要的优化目标。我们采用多目标优化中常用的Pareto 边界分析 [Struct. Multidiscip. Optim., 2010, 41, 853-862] 来确定平衡 MOSFET 的功耗延迟积(PDP)和延迟时间($\tau$)的最佳方案。我们的分析显示,n 型单层 $\mathrm{WSi}_2\mathrm{N}_4$ MOSFETs 位于典型二维材料晶体管的 PDP vs $\tau$ 图中的 Pareto 边界上,表明它们在不同二维材料作为沟道的 MOSFETs 中提供了最佳解决方案之一。

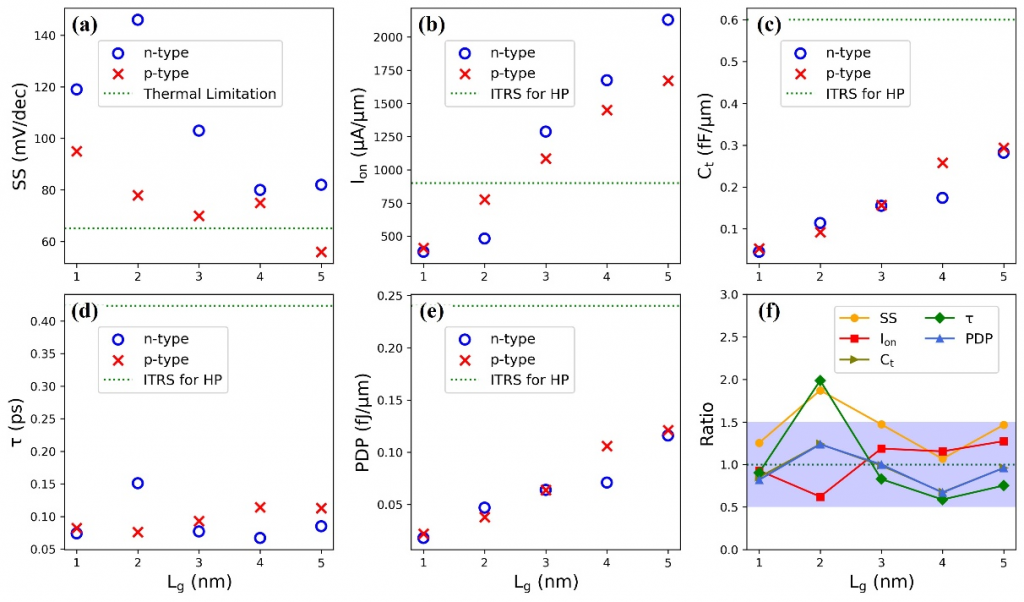

值得注意的是,在 3-5 nm 的栅长范围内,用于高性能应用的n型和p型双栅单层 $\mathrm{WSi}_2\mathrm{N}_4$ MOSFETs 表现出高度对称性,开态电流的比值约为 1.2,其它参数如亚阈值摆幅($SS$)、电容($C_{t}$)、延迟时间($\tau$)、功耗延迟积(PDP)的比值也在 0.5-1.5 范围内。

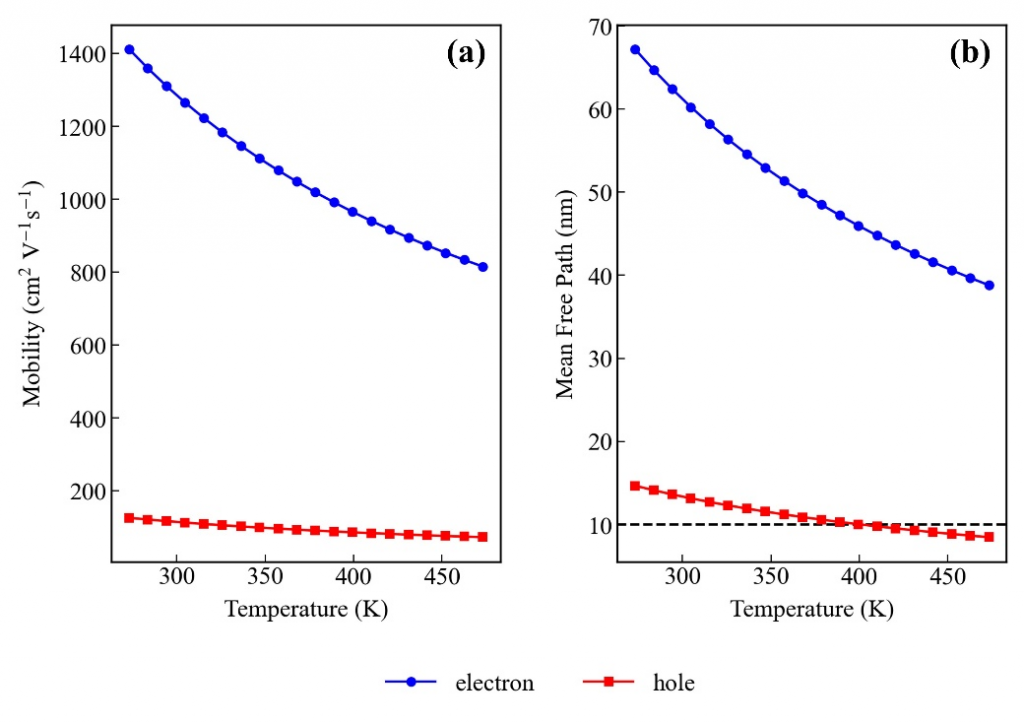

由于模型是基于弹道输运的,通过计算迁移率和平均自由程随温度的变化可以估计模拟结果的适用温度范围。在 400 K 以下,电子与空穴的平均自由程都大于 10 nm,大于文章中模拟的所有器件结构在传输方向的长度,弹道输运的结果是适用的。

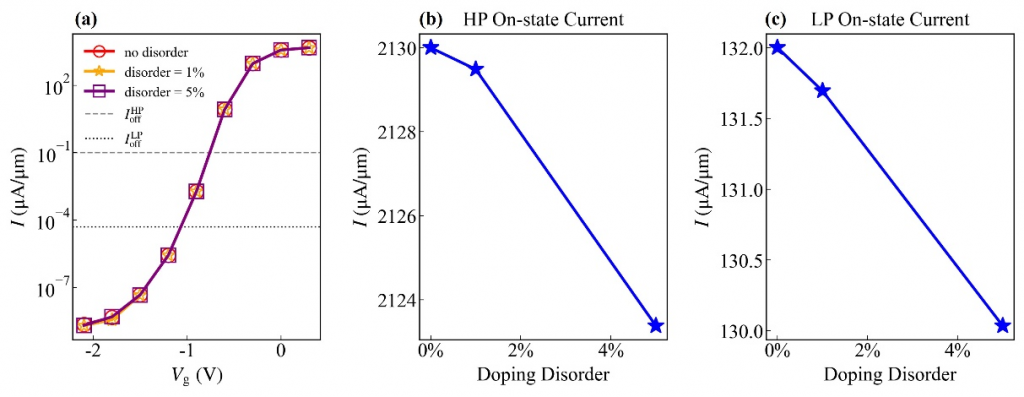

文章中进一步使用高斯分布随机地进行空间掺杂,考虑掺杂无序对输运性质的影响。在掺杂无序度为总体掺杂浓度的 5% 以内时,开态电流随着无序增加而下降,但数值上的变化小于 1%。

总结

本文使用 QuantumATK 材料与器件模拟平台,基于 DFT+NEGF 方法,第一性地模拟了双栅单层 $\mathrm{WSi}_2\mathrm{N}_4$ MOSFETs 在亚 5 nm 栅长下的性能极限。结果显示了 n 型和 p 型高性能器件指标的高度对称性,可用于构建超短沟道同质 CMOS 器件。与相同栅极长度的典型二维材料晶体管相比,n 型单层 $\mathrm{WSi}_2\mathrm{N}_4$ 晶体管取得了最佳的功耗与性能平衡。考虑温度和无序掺杂的影响后,模拟结果仍然适用。

参考文献

Y. Li, C. Qi, X. Zhou, L. Xu, Q. Li, S. Liu, C. Yang, S. Liu, L. Xu, J. Dong et al., Monolayer $\mathrm{WSi}_2\mathrm{N}_4$ : A promising channel material for sub-5-nm-gate homogeneous CMOS devices, Phys. Rev. Appl. 20, 064044 (2023). https://doi.org/10.1103/PhysRevApplied.20.064044