简介

由于环栅(GAA)硅纳米线(NW)场效应晶体管(FET)具有更好的静电栅控能力,它被认为是目前主流硅鳍式晶体管(FinFET)最有潜力的继承者之一。在即将来临的环栅硅纳米线晶体管时代,对硅纳米线晶体管性能极限的探究成为业界关心的问题。本文利用第一性原理量子输运模拟,对一维环栅硅线MOS晶体管的性能极限进行评估,并对其延续摩尔定律的能力给出合理可靠的预测。

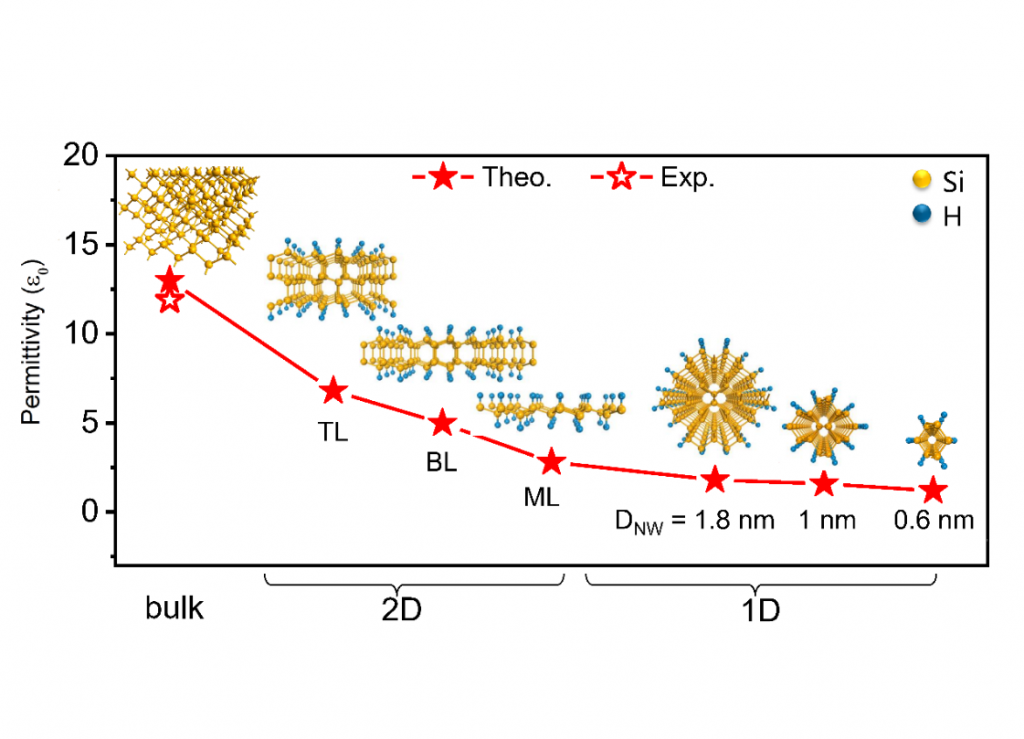

使用环栅结构和足够细的硅纳米线沟道可以保证足够强的栅控,在有效抑制短沟道效应的情况下继续晶体管的尺寸缩放。为了方便描述源漏电极对沟道的影响,这里引入特征长度 $\lambda (\sqrt{\alpha \frac{\varepsilon_{ch}}{\varepsilon_{ox}}t_{ch}t_{ox}})$来表示源漏电场在沟道的穿透深度,其中 α 描述栅极几何结构,在单栅(SG)双栅(DG)、三栅(TG)以及环栅情况下,分别取值 1、1/2、1/3、1/4。$t_{ch}$ 和 $t_{ox}$分别代表沟道和栅氧化物的厚度;$\varepsilon_{ch}$ 和$\varepsilon_{ox}$ 分别代表沟道和栅氧化物的介电常数。如图1所示,从三维体材硅(Bulk Si)到单层硅烷(ML silicane)再到一维硅纳米线(1D Si NW),DFT 计算的介电常数从 $13\varepsilon_{0}$(实验值是 $11.9\varepsilon_{0}$)减小到 $2.8\varepsilon_{0}$ 并最终达到 $1.19\varepsilon_{0}$(0.6 纳米直径)。所以,减小硅纳米线的直径是进一步提升 5 nm 栅长下环栅硅纳米线晶体管性能的尝试方向之一。在实验上,硅纳米线的直径已经缩小到 1 nm。

研究内容

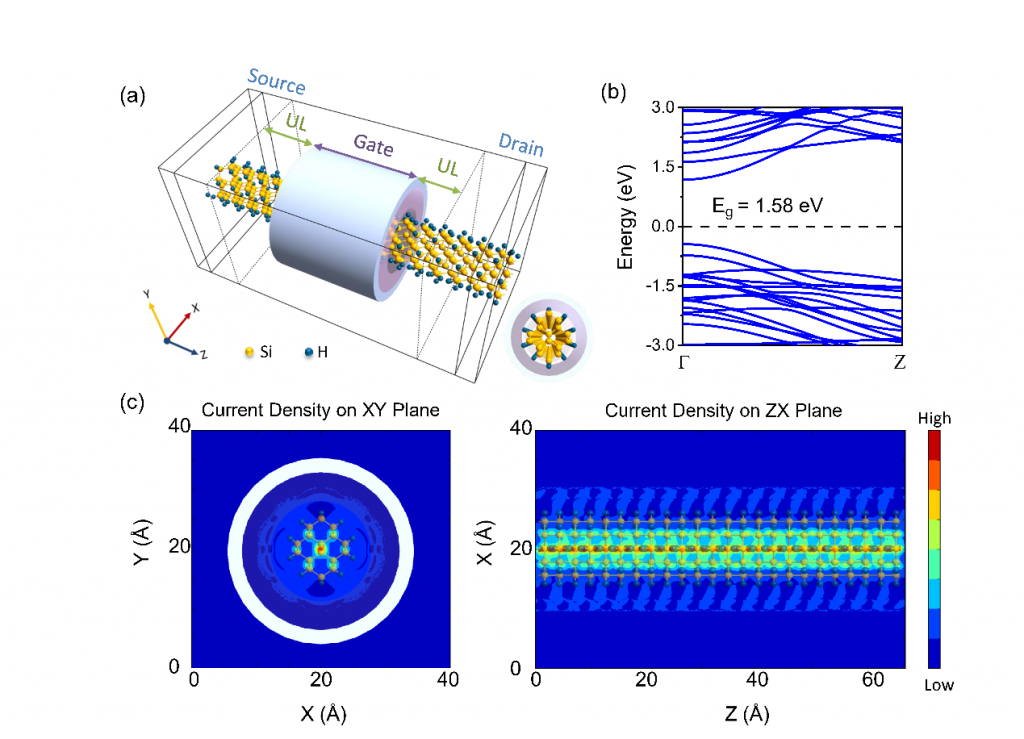

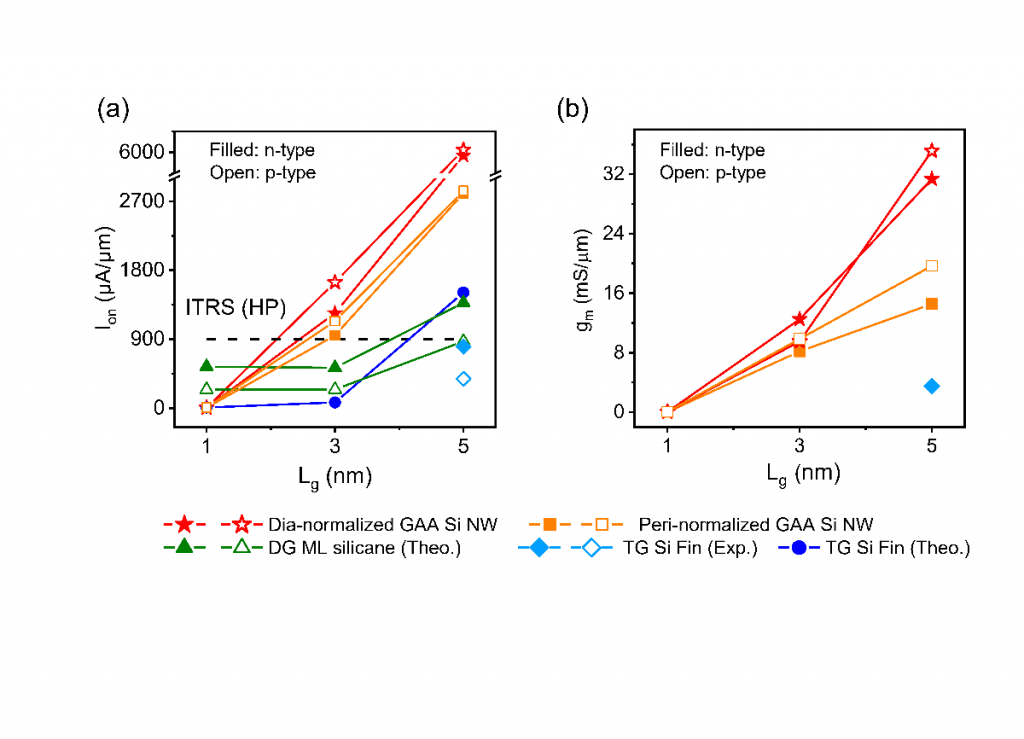

本文选择直径为 1 nm 的硅纳米线作晶体管沟道,模拟了如图 2(a) 所示的环栅硅纳米线晶体管模型。经计算,电流集中在纳米线的中心位置(如图2(c))。因此,除有特殊说明,本文讨论的环栅硅纳米线晶体管电流均为直径归一化处理的结果。如图3所示,在栅长为 5 nm 和 3 nm 的情况下,无论直径还是周长电流归一化方式,环栅硅纳米线晶体管的开态电流都要明显高于理论模拟的三栅硅鳍式晶体管以及双栅单层硅烷晶体管。以 ITRS 要求的高性能器件开态电流为基准,能够满足开态电流标准的三栅硅鳍式晶体管和单层硅烷晶体管,最小栅长均为 5 nm,而达到开态电流标准的环栅硅纳米线晶体管,最小栅长为 3 nm。

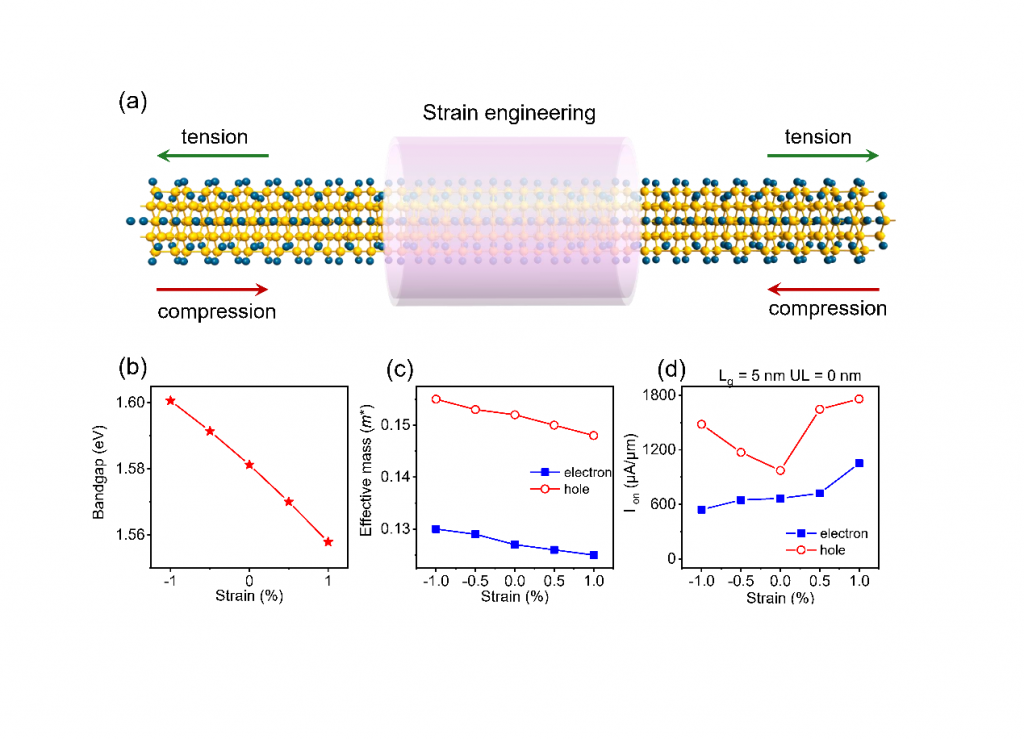

在过去的几十年里,应变工程已经成为硅基器件性能改进的主要解决方案,实验和理论工作都证实了应变可以使硅 p-MOS 晶体管的电流增强 4 倍以上,n-MOS 晶体管的电流增强 2 倍以上。对于以一维硅纳米线为沟道材料的晶体管,应变工程的效果令人期待。本文研究发现,对于 1 nm 直径的硅纳米线,1% 范围内的应力作用只改变直接带隙的大小,并不会引起直接带隙向间接带隙的转变。当应变从 -1%(压缩)到 +1%(拉伸)时,直接带隙从 1.6 eV 减小到 1.55 eV(图4(b));电子(空穴)的有效质量由 0.16(0.13)$m_0$ 降低到 0.15(0.12)$m_0$(图4(c))。值得注意的是,对于 p 型器件,无论是压缩和拉伸对开态电流都有提升作用,且拉伸应变的影响更为明显。在 1% 的压缩和拉伸应变下,p 型器件的开态电流分别提高了 60% 和 80%(图4(d))。

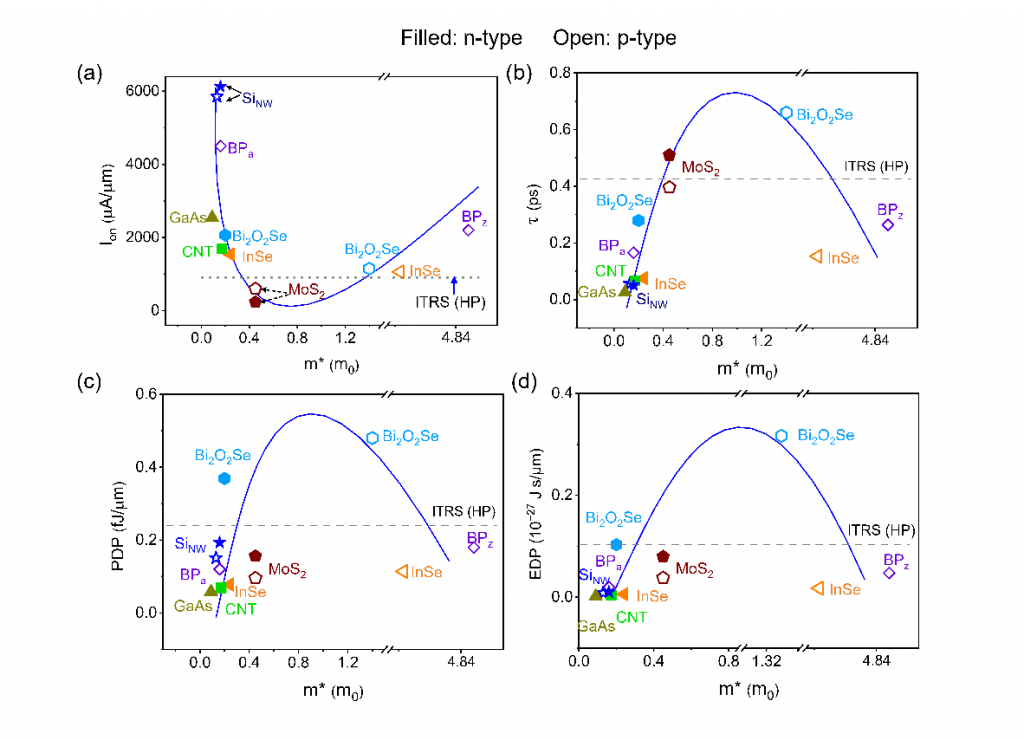

先前的理论工作仅显示了栅长 $L_g$ = 5 nm 的情况下,典型低维 FET 的 $m^*$ 和 $I_{on}$ 之间的关系。即当 $m^*$ 逐渐增大时,开电流 $I_{on}$ 将先减小后增大,转折点位于 0.8 $m_{0}$。原因是小 $m^*$ 引起的高输运速度和大 $m^*$ 造成的高态密度都可以提供高 $I_{on}$。当 $L_g$ 为 5 nm 时,$D_{NW}= 1 $ nm 的 n 型和 p 型 GAA Si NWFET 也遵循这样的 $I_{on}$—$m^*$ 关系。此外,本文首次总结了延迟时间、功耗和功耗延迟积随 $m^*$ 变化的关系:这三项性能参数均随着 $m^*$ 的增加先增加再减少(图5)。有趣的是,它们的转折点都出现在 0.8 $m_{0}$ 左右。这些总结的器件性能趋势将为预测高性能低功耗晶体管提供更全面的指导。

总结

本文报道的工作利用第一性原理方法探究了环栅硅纳米线晶体管的性能极限。与类似尺寸的三栅 Si NW FinFET 相比,GAA Si NWFET 在相同栅长下的性能更优。并且,应变工程可进一步增加其开电流。该研究显示了 GAA-Si NWFET 在亚 3 nm 栅极长度区域的巨大潜力。

参考

- Shiqi Liu, Qiuhui Li, Chen Yang, Jie Yang, Linqiang Xu, Lin Xu, Jiachen Ma, Ying Li, Shibo Fang, Baochun Wu, Jichao Dong, Jinbo Yang, Jing Lu, Performance Limit of Gate-All-Around Si Nanowire Field-Effect Transistors: An Ab Initio Quantum Transport Simulation. Phys. Rev. Appl., 18, 054089 (2022).

- 本文涉及的全部研究内容均使用 QuantumATK软件 完成。