研究背景

随着传统硅基场效应晶体管(FET)器件尺寸不断缩小,器件功耗和亚阈值摆幅(Subthreshold Swing, SS)问题愈发突出,传统 MOSFET 已难以满足低功耗、高性能逻辑电路的需求。为突破硅基器件的物理极限,新型二维材料及其异质结构被广泛研究,尤其是石墨烯和过渡金属二硫化物(TMDs)等材料。石墨烯因其高载流子迁移率和零带隙的特性,可用作 Dirac 源极实现高效率载流子注入,而 MoS2 等半导体二维材料具有可调节的带隙和优异的开关性能,将其与石墨烯横向连接形成异质结,可同时兼具高开态电流与低亚阈值摆幅的优势。近年来,Dirac 源-FET(DSFET)作为新型低功耗器件方案受到了广泛关注,但器件性能受限于源极掺杂浓度、能带匹配以及界面载流子传输效率等因素,如何通过优化异质结构设计实现陡坡开关、低功耗高性能仍是亟需解决的关键问题。本研究通过构建横向石墨烯/MoS2 异质结构,系统分析源极掺杂对器件亚阈值特性和开态电流的影响,为二维材料 FET 的设计提供了理论指导。

研究内容

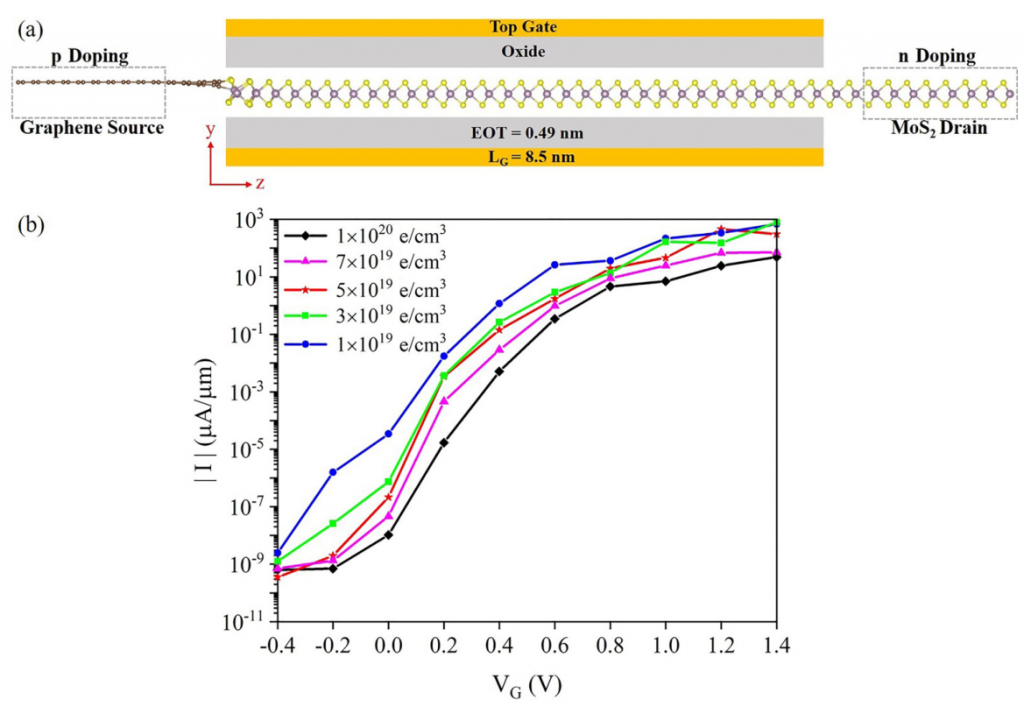

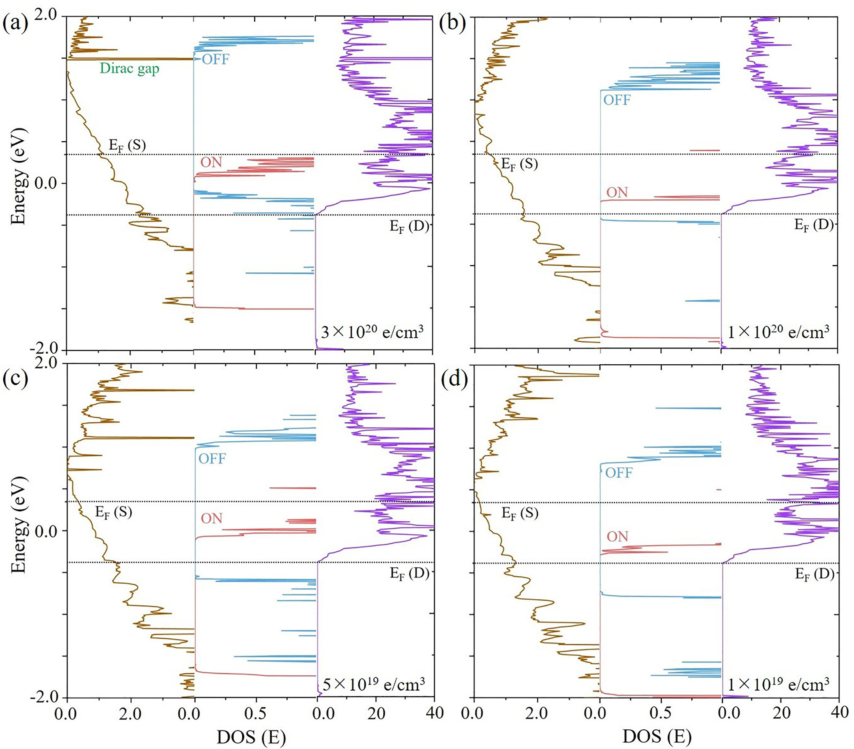

基于第一性原理计算和量子输运模拟,我们系统地研究了基于横向 graphene/MoS2 异质结构的 Dirac-源场效应晶体管(DSFET)的输运特性。首先,由于石墨烯源的掺杂浓度会显著影响界面的能带对齐,从而影响 DSFET 的性能。因此,考虑六种不同的石墨烯源掺杂浓度并计算电流-电压输运特性曲线。

我们发现过低的掺杂浓度会减少开态下从石墨烯源极注入的载流子浓度,不利于开态电流。因此,石墨烯源极的适度掺杂浓度对于石墨烯/二硫化钼界面的理想能带排列至关重要,这有利于实现高开态电流和陡峭的 SS 值。

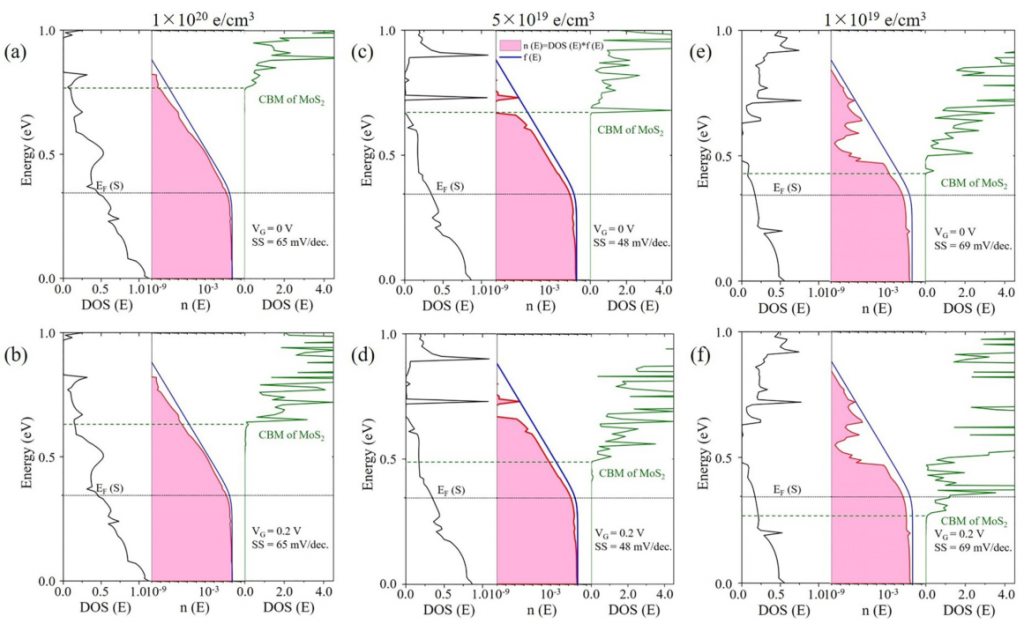

为更好地理解不同源极掺杂浓度下亚阈值摆幅(SS)值的差异,在图 3 中展示了石墨烯源极的态密度(DOS)、源极载流子浓度分布以及 MoS2 沟道在亚阈值区域的态密度。亚阈值摆幅值变化最陡峭的亚阈值区域对应于栅极电压从 0 到 0.2 V 的范围(从关态到开态)。在源极载流子浓度高达 1×10²⁰e/cm³ 时,石墨烯源极的狄拉克点远高于器件的费米能级。

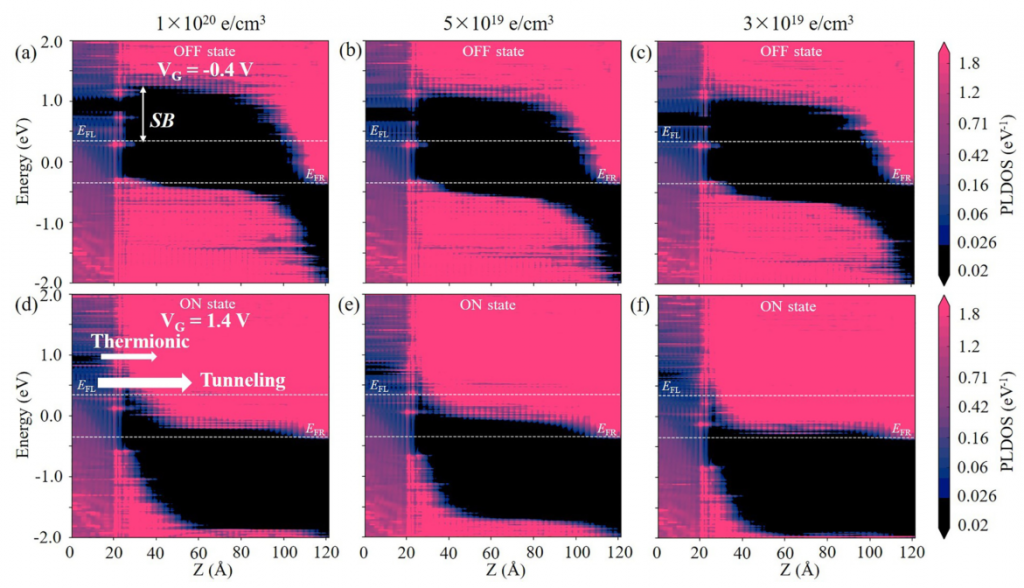

一方面,由于界面态的钉扎作用,器件从关态(OFF)到开态(ON)时的界面肖特基势垒(SB)略微降低,电流增加主要归因于 SB 变薄;另一方面,界面态在开态通过三角形 SB 缩短了隧穿路径,从而增强了开态电流。

总结

本文基于第一性原理计算和量子输运模拟,系统研究了横向 graphene/MoS2 异质结构 Dirac-源场效应晶体管(DSFET)的输运性能。研究表明,通过调控石墨烯源极掺杂浓度,可在保持高开态电流的同时,实现极低的亚阈值摆幅(SS),器件性能满足国际半导体技术路线图对低功耗器件的要求。分析指出,源极掺杂浓度过高或过低均会导致界面能带不匹配,从而降低 SS 和开态电流。此外,界面态对器件性能存在双重作用:一方面通过钉扎效应略微降低肖特基势垒(SB),另一方面在开态通过三角形 SB 缩短隧穿路径,增强开态电流。研究还总结了横向异质结构 Dirac-源晶体管的工作机制,为二维材料异质结构 DSFET 的设计提供了理论指导。总体而言,该工作为实现低功耗、高性能的新型 FET 提供了可行的设计策略,并推动二维材料在下一代电子器件中的应用发展。

参考文献

- Song S, Lyu J, Qin L, et al. Lateral graphene/MoS2 heterostructures for steep-slope Dirac-source field-effect transistors[J]. Physical Review B, 2024, 110(12): 125407.

- https://doi.org/10.1103/PhysRevB.110.125407