研究背景

随着集成电路特征尺寸持续向纳米甚至原子级别缩小,传统铜互连材料在高密度三维集成和垂直互连结构中的导电性能正面临严峻挑战。器件微缩导致的尺寸效应、界面散射与量子输运问题,使得金属互连的电阻率急剧上升,严重限制了器件的速度与能效。因此,寻找具有低界面电阻、高导电性和稳定尺寸标度行为的新型材料体系已成为先进互连技术的重要研究方向。

近年来,拓扑半金属因其独特的能带结构和高载流子迁移率,成为下一代电子互连材料的潜在候选。拓扑半金属在费米能级附近存在线状或点状狄拉克态,其电子输运特性受拓扑保护,能够显著抑制界面散射,从而在纳米尺度下保持较低的电阻率。这一特性为突破传统金属互连的性能瓶颈提供了新的可能。

然而,在器件实际应用中,界面效应仍是决定互连电阻的关键因素。随着器件尺寸的不断缩小,界面电阻率不再是常数,而表现出明显的标度行为,即其值随通道长度、厚度或界面粗糙度等几何参数变化而改变。理解并量化拓扑半金属界面的电阻率标度规律,对于准确评估其在垂直互连结构中的导电性能至关重要。

研究内容

本研究聚焦于拓扑半金属界面电阻率的标度行为及其在垂直互连体系中的应用。通过理论分析与计算模拟,探讨不同拓扑半金属在界面处的电子输运特征及尺寸依赖规律,旨在揭示拓扑保护态在降低界面散射、保持电阻稳定性方面的作用机制。这一研究不仅为理解拓扑材料的界面输运提供了新的物理图景,也为设计高性能、低功耗的三维互连结构提供了理论基础。

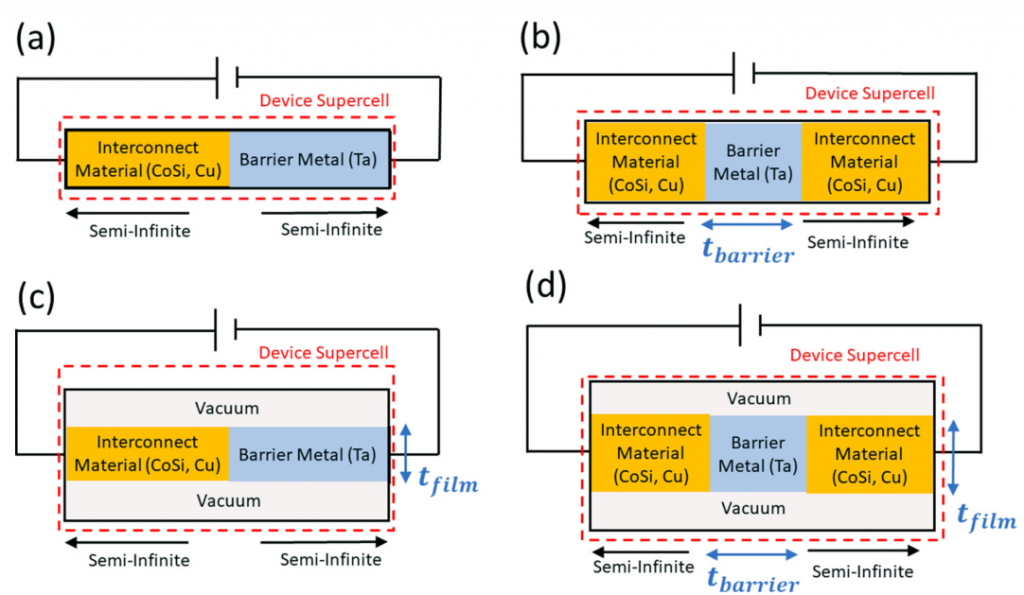

对于单界面和双界面模型两种结构,考虑电子在体和薄膜中的传输,并通过在垂直于传输方向上添加真空来模拟。

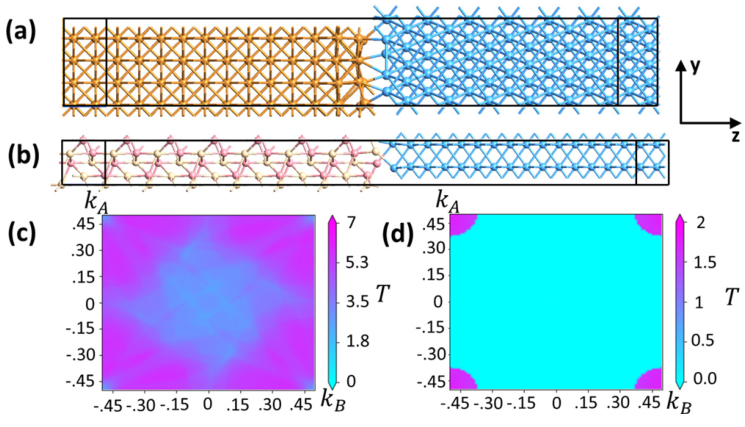

k 分辨透射谱显示 Cu/Ta 界面的透射谱透射率可达 T= 7 的区域,而靠近 Γ 点处透射率较低。CoSi/Ta 界面的透射谱在 BZ 边界有 4 个小的 T= 2 的区域,而其他地方的透射谱为零。CoSi/Ta 界面结构的低透射率是由于 BZ 中 CoSi 的体电子态密度(DOS)极低,集中在区角的 Weyl 节点附近。与 Cu 相比,CoSi/Ta 界面上的低电子透射率转化为高比电阻率。

从计算的域态密度(LDOS)可以发现,对于 Cu/Ta 界面是均匀的 LDOS,在薄膜表面附近没有明显变化。然而,在 CoSi/Ta 界面,Ta 区域的 LDOS 分布均匀,但在 CoSi 表面处 LDOS 强烈局域化,CoSi 内部区域的 LDOS 几乎为零。这是由于存在的 Weyl 节点和由此产生的拓扑保护表面态从布里渊带的中心延伸到角落,在 CoSi 薄膜中产生相对较少的靠近费米能级的体态和大量的导电表面态所导致的。

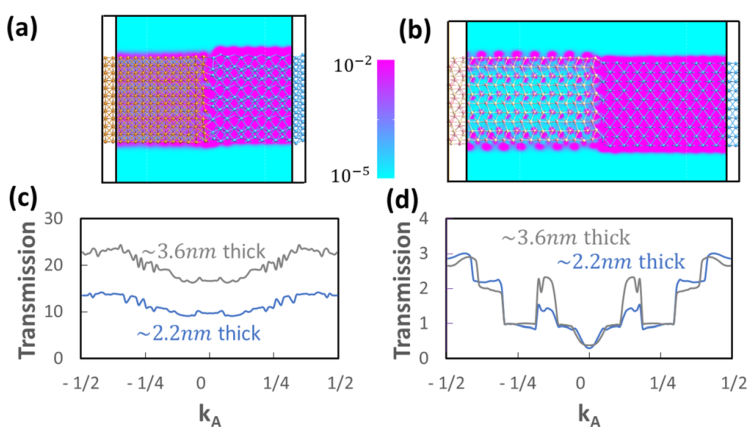

从计算的动量分辨电子透射谱可以发现,对于 Cu/Ta,使薄膜更厚(从 2.2 到 3.6 nm)只是增加了总电子透射,因为更厚的薄膜有更多的原子,从而有更多的电子,这有助于传导;对于 CoSi/Ta 薄膜,随着薄膜变厚,观察到几乎相同的透射率。这是因为 CoSi 中表面主导的电子输运对薄膜厚度不敏感,因为体载流子的增加与表面载流子相比相对较小。

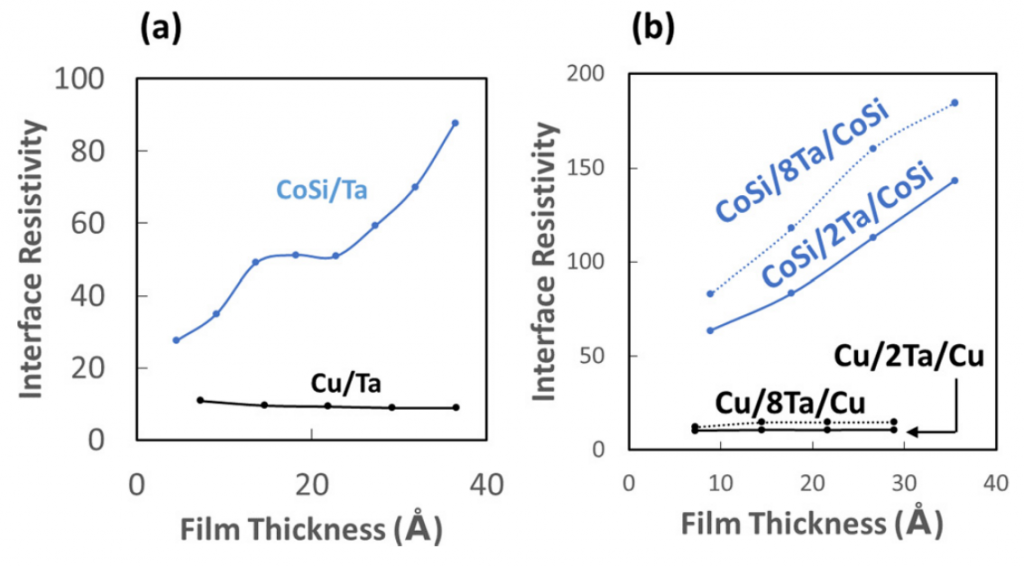

评估 Cu/Ta 和 CoSi/Ta 结构中电阻率随薄膜厚度的变化情况。对于单界面结构,Cu/Ta 界面电阻率随薄膜厚度的变化不大,这表明大部分传导发生在薄膜内部,仅在表面有少量贡献。然而,对于 CoSi/Ta,界面电阻率随薄膜厚度减小而降低。随着 CoSi/Ta 薄膜变薄,高导电性的表面在总传输中的贡献变大,而高电阻率的体部贡献变小。对于双界面结构,其物理原理基本相同,只是电子必须穿透两个界面以及有限的 Ta 区域,而不仅仅是单个界面。Ta 层的厚度对其影响较小,两原子层(2 Ta)的情况显示出的界面电阻率略低于八原子层(8 Ta)的情况,这可能是由于左右 CoSi 电极之间的直接波函数重叠更大所致。

总结

本文研究了 Cu/Ta 和 CoSi/Ta 界面处的电子散射特性,分别作为金属/金属界面和拓扑半金属/金属界面的代表体系,以期用于先进互连应用。研究结果表明,由于拓扑半金属在费米能级附近具有较低的体电子态密度,其体相界面电阻率在 CoSi/Ta(半金属/金属)界面中比 Cu/Ta(金属/金属)界面高出一个数量级以上。对于包含界面的薄膜结构,普通金属之间(Cu/Ta)的界面比电阻几乎不随薄膜厚度变化;而拓扑半金属与金属之间(CoSi/Ta)的界面电阻率则会随着薄膜厚度减小而下降。此外,在薄膜体系中,拓扑半金属/金属界面的比电阻值相对于体相结果低出超过一个数量级。这些差异可归因于:在拓扑半金属 CoSi 薄膜中,电子输运主要由表面态主导,而在普通金属薄膜中则仍表现为体态输运。这一结果表明,拓扑半金属在作为下一代互连导体材料方面具有巨大潜力,尤其适用于那些尺寸极小、界面普遍存在且电阻瓶颈日益突出的先进集成电路互连结构。

参考文献

- Lanzillo, Nicholas A., Utkarsh Bajpai, and Ching-Tzu Chen. “Topological semimetal interface resistivity scaling for vertical interconnect applications.” Applied Physics Letters 124.18 (2024).

- https://doi.org/10.1063/5.0200403