文章使用密度泛函理论研究了肖特基势垒高度(Schottky Barrier Height)对界面形态的依赖,以及如何通过在 NiSi2/Si界面替位掺杂进行调制。使用 meta-GGA 交换相关泛函预测出相当精确的Si带隙。本文的研究表明,(n型半导体的)电子肖特基势垒高度在(001)方向显著低于(111)方向。这些结果定性上与界面形态依赖的肖特基势垒高度的实验结果一致。肖特基势垒高度能够通过 NiSi2/Si 界面替代掺杂显著降低,本文讨论了 Si 掺杂位点、杂质类型以及晶向对优化肖特基势垒高度的影响。

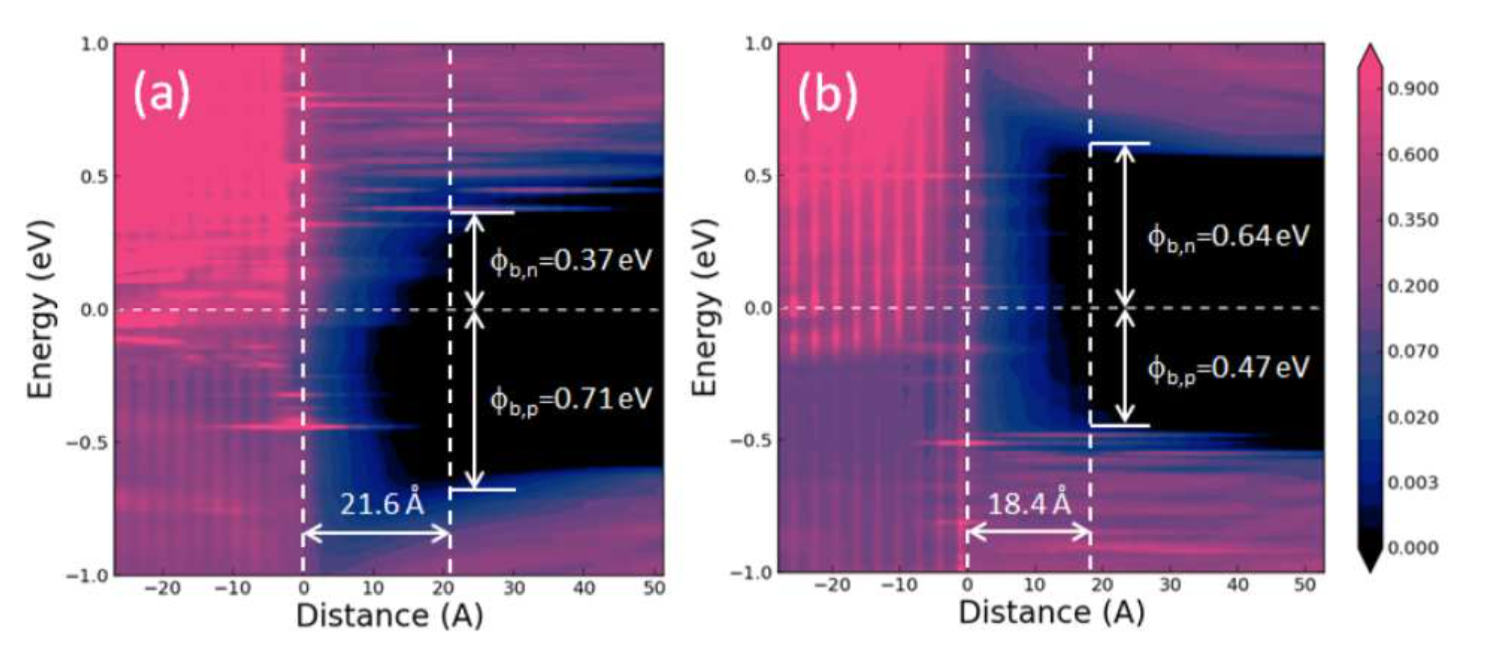

Fig. 2. Contour plots of LDOS on intrinsic (a) NiSi2/(001)Si and (b) NiSi2/(111)Si where the interface between NiSi2 and Si located at 0 Schottky Barrier Height is extracted at z=21.6 Å and z=18.4Å away from the interface fro (a) and (b), respectively, where the LDOS at Fermi level becomes small enough. Extracted Schottky Barrier Heights for electrons and holes are denoted as Φb,n and Φb,p, respectively